# ARTICLE

# A Nonvolatile Memory Device Made of a Ferroelectric Polymer Gate Nanodot and a Single-Walled Carbon Nanotube

Jong Yeog Son,<sup>†</sup> Sangwoo Ryu,<sup>†</sup> Yoon-Cheol Park,<sup>†</sup> Yun-Tak Lim, Yun-Sok Shin,<sup>†</sup> Young-Han Shin,<sup>‡,</sup>\* and Hyun Myung Jang<sup>†,</sup>\*

<sup>†</sup>Department of Materials Science and Engineering, and Division of Advanced Materials Science, Pohang University of Science and Technology (POSTECH), Pohang 790-784, Korea, and <sup>‡</sup>Department of Physics, University of Ulsan, Ulsan 680-749, Korea

n the past decade, carbon nanotubes (CNTs) have been extensively investigated for their applications to various fields, including field-effect transistors (FETs), electron field emitters, and hydrogen storage.<sup>1-8</sup> Both single-walled CNTs (SW-CNTs) and multiwalled CNTs (MW-CNTs) show high current-carrying capabilities and excellent carrier mobility with a small band gap.<sup>6</sup> A SW-CNT is a seamlessly wrapped single graphene sheet formed into a cylindrical tube, and a MW-CNT is composed of multiple rolled layers of graphene. Both types of CNTs have high Young's moduli and tensile strengths with excellent flexibilities, demonstrating their potentials as candidates for channel materials of the next generation FETs.<sup>7</sup>

Ferroelectric FETs (FeFETs) are nonvolatile random access memory (NVRAM) architectures with a small size and a low operating voltage coupled with fast operation.<sup>8–11</sup> Though Pb-based perovskites, such as Pb(Zr,Ti)O<sub>3</sub> (PZT), exhibit excellent ferroelectric properties, lead toxicity is a major disadvantage for their applications to FeFETs.<sup>12,13</sup> Therefore, many researchers have developed lead-free ferroelectrics.14-18 Among these, ferroelectric copolymers such as poly(vinylidene fluoride-rantrifluoroethylene) (PVDF-TrFE) have been attractively studied because of their low crystallization temperatures, flexibilities, and nontoxicities.15-17

Ferroelectric nanostructures have been fabricated by exploiting various techniques, including anodizing electron-beam lithography, aluminum oxide nanotemplates, and a Si mold for PVDF-TrFE nanodots.<sup>17,19,20</sup> Currently, CNT-based FETs combined with ferroelectric nanostructures do not achieve a truly nanoscale dimension. Therefore, it is **ABSTRACT** We demonstrate a field-effect nonvolatile memory device made of a ferroelectric copolymer gate nanodot and a single-walled carbon nanotube (SW-CNT). A position-controlled dip-pen nanolithography was performed to deposit a poly(vinylidene fluoride-ran-trifluoroethylene) (PVDF-TrFE) nanodot onto the SW-CNT channel with both a source and drain for field-effect transistor (FET) function. PVDF-TrFE was chosen as a gate dielectric nanodot in order to efficiently exploit its bipolar chemical nature. A piezoelectric force microscopy study confirmed the canonical ferroelectric polarization states with the stable current retention and fatigue-resistant characteristics make the present PVDF-TrFE-based FET suitable for nonvolatile memory applications.

**KEYWORDS:** ferroelectric polymer nanodot · carbon nanotube · field-effect transistor · nonvolatile memory device

highly desirable to develop a new fabrication technique that can readily handle nanostructures with positional controllability. Dip-pen nanolithography (DPN) technology based on scanning probe microscopy enables the production and handling of various nanostructure materials, including polymers and semiconductors.<sup>21–23</sup> In particular, a recently reported DPN of PbTiO<sub>3</sub> nanodots provided the production and handling of a ferroelectric nanostructure at a desired position with nanometerscale accuracy.<sup>23</sup> In spite of extensive research efforts on DPN, however, it has not been successfully implemented in the practical realization of a nanoscaled nonvolatile memory device.

In the present study, a nanometer-scale NVRAM device made of a ferroelectric PVDF-TrFE nanodot and a SW-CNT channel is demonstrated by suitably exploiting the DPN method. The PVDF-TrFE nanodot was chosen as a gate dielectric to efficiently exploit its bipolar chemical nature. In addition, a polymer gate rather than an inorganic oxide gate was adopted by considering its chemical affinity (*i.e.*, low interfacial tension) toward the CNT channel with a

\*Address correspondence to hmjang@postech.ac.kr, hoponpop@ulsan.ac.kr.

Received for review August 24, 2010 and accepted October 28, 2010.

**Published online November 4, 2010.** 10.1021/nn1021296

© 2010 American Chemical Society

VOL. 4 • NO. 12 • 7315-7320 • 2010

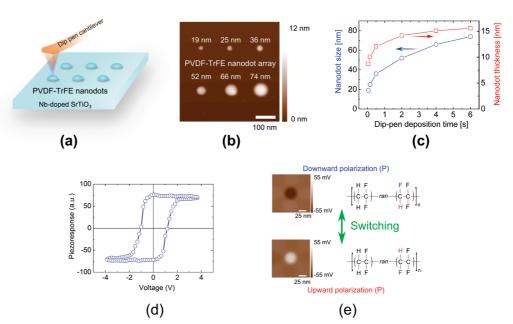

Figure 1. PVDF-TrFE nanodots prepared by dip-pen nanolithography (DPN). (a) Fabrication of PVDF-TrFE nanodots on a Nbdoped SrTiO<sub>3</sub> substrate using the DPN method. (b) AFM image of various PVDF-TrFE nanodots formed on a Nb-doped SrTiO<sub>3</sub> substrate. (c) Nanodot size (diameter and thickness) plotted as a function of the dip-pen deposition time. (d) Piezoelectric hysteresis loop of the PVDF-TrFE-gate nanodot with a diameter of 19 nm. Piezoelectric characteristics were examined by exploiting piezoelectric force microscopy (PFM). (e) Two PFM images of the PVDF-TrFE-gate nanodot with a diameter of 19 nm. The top and bottom PFM images correspond to the downward and upward polarizations, respectively. A bipolar chemical nature of PVDF-TrFE is schematically depicted in the right-hand-side figure using two distinct orientations of the proton (H<sup>+</sup>) in a TrFE unit.

minimum concentration of interfacial defects.<sup>15</sup> By fully utilizing the nanometer-scale controllability of the DPN method,<sup>23</sup> we have successfully formed a PVDF-TrFE nanodot gate precisely at the center of the SW-CNT channel. This polymer-gate-based FeFET shows desirable memory effects that are suitable for NVRAM applications.

# **RESULTS AND DISCUSSION**

Figure 1a schematically depicts the formation of polymer nanodots on a Nb-doped SrTiO<sub>3</sub> substrate by the DPN method. PVDF-TrFE nanodots were made by serial procedures composed of dipping the precursor sol, drying, and annealing at 140 °C for 1 h.<sup>15-17,24,25</sup> Figure 1b shows an atomic force microscope (AFM) image of the DPN-formed nanodots with various diameters. The dimension (diameter, thickness) of the nanodot is precisely controlled by adjusting the dip-pen deposition time (Figure 1c). A piezoelectric hysteresis loop of the nanodot having a diameter of 19 nm demonstrates the switching of ferroelectric polarization (Figure 1d). Because of a bipolar chemical nature of PVDF-TrFE polymer, the polarization switching can be achieved by swapping the fluorine anion  $(F^{-})$  with the proton  $(H^{+})$ counterpart in a TrFE unit (Figure 1e).

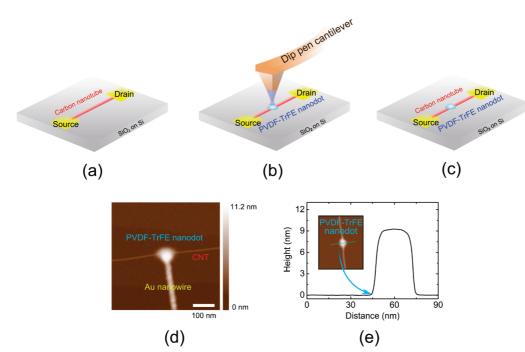

The DPN fabrication of the PVDF-TrFE-based FeFET is schematically depicted in Figure 2. A source and drain were prepared from gold electrodes at both ends of the SW-CNT channel using an electron-beam lithography technique (Figure 2a). Then, a PVDF-TrFE nanodot was suspended at the center of the CNT channel by dip-

pen lithography (Figure 2b). We subsequently embodied a polymer nanodot-based CNT-FeFET memory device in which all of the components were integrated into a single piece within a nanometer scale (Figure 2c). Figure 2d presents an AFM image of the PVDF-TrFEdeposited SW-CNT. In Figure 2d, a Au-metal gate was fabricated on the PVDF-TrFE-gate nanodot using the DPN method. A fairly straight SW-CNT was observed on the SiO<sub>2</sub>/Si substrate. In addition, well-aligned terraces were observed, indicating an atomically flat surface of the SiO<sub>2</sub>/Si substrate with the rms (root-mean-square) roughness of less than 0.1 nm. The PVDF-TrFE nanodot with a diameter of 28 nm was formed exactly at the center of the SW-CNT, demonstrating nanometer-scale controllability of the present DPN technology. The surface line profile presented in Figure 2e indicates that the thickness of the PVDF-TrFE nanodot is approximately 9.2 nm. This nanometer-sized gate has further applications to high-density data storage with a storage capacity of  $\sim$ Tbit/inch<sup>2</sup> (refs 8 and 17).

The ferroelectric properties of the PVDF-TrFE copolymer nanodot were investigated by utilizing piezoelectric force microscopy (PFM). Prior to the PFM measurement, the ferroelectric polymer nanodot was electrically polarized by applying a bias voltage of  $\pm 5$  V. PFM images of the ferroelectric polymer nanodot were obtained for both upward and downward polarizations (before depositing the Au-metal gate onto the polymer nanodot). During the switching process, a bias voltage of  $\pm 5$  V was applied through the conducting PFM tip by simultaneously grounding the source, drain, and

SNANO

Figure 2. Schematic drawings on the DPN fabrication of the PVDF-TrFE-based FeFET device and associated AFM images. (a) Preparation of a source and drain at both ends of the SW-CNT channel deposited onto a SiO<sub>2</sub>/Si substrate. (b) Formation of the PVDF-TrFE-gate nanodot using the DPN method. (c) Ferroelectric FET composed of the SW-CNT channel and the PVDF-TrFE-gate nanodot suspended at the center of the CNT channel. (d) AFM image of the CNT-based nonvolatile memory device, entirely composed of nanostructured elements. (e) Surface line profile across the PVDF-TrFE nanodot region.

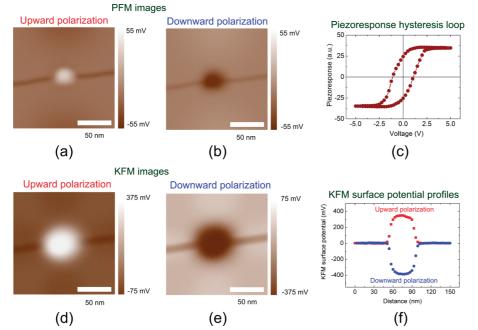

Si substrate. In the PFM image, the upward polarization (Figure 3a) is clearly distinguished from the downward polarization (Figure 3b). The piezoelectric hysteresis loop presented in Figure 3c demonstrates a switching of the ferroelectric polarization with a coercive voltage of  $\sim$ 1.2 V. The coercive voltage of the PVDF-TrFE film having the same thickness of  $\sim$ 10 nm (thus, coercive field) is approximately 2.1 V and, thus, is substantially higher than that of the PVDF-TrFE nanodot (Supporting Information). A Kelvin force microscopy (KFM) image of the nanodot for the upward polarization (Figure 3d) is clearly distinguished from that

Figure 3. PFM and KFM data of the PVDF-TrFE-gate nanodot deposited onto the SW-CNT channel. A PFM image for the upward polarization (a) is clearly distinguished from that for the downward polarization (b). (c) Piezoelectric hysteresis loop of the PVDF-TrFE-gate nanodot demonstrating the switching of the ferroelectric polarization at an applied bias voltage of  $\sim$ 1.2 V. KFM images of the PVDF-TrFE nanodot region are presented for both (d) upward and (e) downward polarizations. (f) Measured KFM surface potential plotted as a function of the lateral distance along the CNT channel.

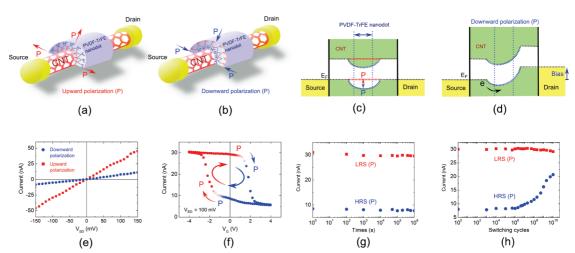

Figure 4. NVRAM characteristics of the PVDF-TrFE-gate FET memory device. Schematic drawings that show a bipolar chemical nature of the PVDF-TrFE-gate nanodot: (a) upward and (b) downward polarizations. (c) Band diagram that schematically illustrates the operation principle of the PVDF-TrFE-gate-based FET. Tunneling contacts between the SW-CNT and the Au electrodes are indicated by two black vertical lines. (d) Schematic band diagram illustrating the effect of a positive bias field on the band structure across the CNT channel. (e) Measured current values plotted as a function of the source-drain voltage ( $V_{SD}$ ) for both upward and downward polarizations. (f)  $I_{SD}-V_G$  transfer curve of the PVDF-TrFE-based FET memory device at a fixed value of  $V_{SD} = 100$  mV. (g) Two retained  $I_{SD}$  states plotted as a function of the relaxation time. (h) Fatigue-test result of the PVDF-TrFE-based FET memory device.

of the downward polarization (Figure 3e). The measured KFM surface potential is plotted in Figure 3f as a function of the lateral distance along the CNT channel. The KFM surface potential clearly splits into two distinct values (+380 and -400 mV) at the PVDF-TrFE nanodot region, which demonstrates the polarization switching between the downward and upward states.

The bipolar chemical nature of the PVDF-TrFE gate is schematically depicted in Figure 4a,b for the two distinct polarization states. The electronegative fluorine anions (F<sup>-</sup>) in the PVDF-TrFE cover the CNT surface in the upward polarization (Figure 4a), whereas the protons (H<sup>+</sup>) are oriented toward the CNT surface in the downward polarization (Figure 4b). In Figure 4a,b, the upward polarization corresponds to a negative gate bias, while the downward polarization corresponds to a positive bias voltage.<sup>15</sup> PVDF-TrFE was deliberately chosen in order to exploit its bipolar chemical nature for controlling the gate current via the bias voltage. Figure 4c,d schematically describes the operation principle of the present PVDF-TrFE-gate-based FeFET. Due to a difference in the work functions between the CNT and the PVDF-TrFE gate dielectric, the downward polarization (+V gate; marked with a blue arrow) induces a band bending (blue dots) at the gate region (Figure 4c), which leads to a highly resistive state. Alternatively, the upward polarization (-V gate; red arrow) effectively flattens the band, resulting in a metal-like behavior.<sup>1</sup> An applied positive bias voltage does build up a chemical potential gradient between the source and drain (Figure 4d). This consequently suppresses the barrier or the degree of band bending slightly, which results in an increased current density under a positive bias field.<sup>1</sup>

The NVRAM characteristics of the present polymergate FET memory device were experimentally examined. Figure 4e presents the measured current values plotted as a function of the source-drain voltage  $(I-V_{SD} \text{ curve})$  for both upward and downward polarizations of the ferroelectric PVDF-TrFE nanodot. In the measurement, the conducting AFM tip was entirely removed after electrically polarizing the gate nanodot. As shown in Figure 4e, the PVDF-TrFE-gate FET exhibits two distinct linear  $I - V_{SD}$  curves with different slopes, distinguishing the high resistance state (HRS) from the low resistance state (LRS).<sup>1,5</sup> Figure 4f presents the  $I_{SD} - V_G$  transfer curve which indicates a p-type Schottky barrier in the present FeFET. The hole carrier mobility is estimated to be about 150  $\mbox{cm}^2\,\mbox{V}^{-1}\,\mbox{s}^{-1}$  (refs 1 and 2). On the basis of the upward polarization (i.e., -Vgate), the polymer-gate FET exhibits an LRS in the  $I-V_{SD}$ curve with a resistance value of approximately 3.3 M $\Omega$ . On the contrary, the FET for the downward polarization (+V gate) is characterized by a HRS with a resistance as high as  $\sim$ 13.7 M $\Omega$ . These two distinct resistivity characteristics depending on the bias voltage can exploit the present PVDF-TrFE-gate nanodot structure for applications to CNT-based NVRAM devices in which all of the components are integrated into a single nanometer-sized piece. In addition, the  $I-V_{SD}$  current of the HRS (downward polarization) can be significantly reduced by adopting a PVDF-TrFE-gate nanodot with a diameter greater than 28 nm (Supporting Information).

To assess the device reliability of the PVDF-TrFEbased FET toward NVRAM applications,<sup>10</sup> we have examined data retention and electrical fatigue characteristics. The  $V_{SD}$  value was fixed at 100 mV to evaluate the source-drain current ( $I_{SD}$ ). As shown in Figure 4g, the

7318

bistable currents of the LRS and HRS are well retained up to  $10^6$  s, demonstrating a desirable retention property of the present FET device. The fatigue resistance is another important criterion in NVRAM applications as it represents a resistance against the  $I_{SD}$  degradation which arises from repeated writing and erasing operations. The fatigue resistance characteristics were examined using a triangular bipolar bias of 5 V at 1 kHz as the repetition switching bias. Though the current value of the HRS increases rather rapidly at a certain critical value of the switching cycle (~10<sup>8</sup>), the PVDF-TrFEbased FET exhibits acceptable memory characteristics (*i.e.*, two separate current states) up to ~10<sup>10</sup> switching cycles (Figure 4h).

# CONCLUSIONS

A nonvolatile random access memory (NVRAM) device made of a ferroelectric polymer-gate nanodot and a single-walled CNT was demonstrated. By exploiting the DPN method, a PVDF-TrFE polymer nanodot was formed at a desired position on a CNT channel. This polymer-gate nanodot enables us to establish two distinct resistivity characteristics depending on its ferroelectric polarization, with the low and high resistance states corresponding to the upward and downward polarizations, respectively. The bistable currents with a desirable retention property and the fatigue resistance make the present PVDF-TrFE-based FET suitable for nonvolatile memory applications.

### METHODS

A nonvolatile memory device was fabricated to have a singlewalled CNT and a gate ferroelectric copolymer, poly(vinylidene fluoride-ran-trifluoroethylene) (PVDF-TrFE). For this purpose, SiO<sub>2</sub>/Si substrates were first prepared by the Radio Corporation of America (RCA) cleaning and thermal oxidation. The thickness of the thermally grown SiO<sub>2</sub> layer was estimated to be 20 nm. The SW-CNTs prepared by plasma-enhanced chemical vapor deposition were sonicated into a dispersion using dichloroethane. A source and drain made of gold electrodes were prepared at both ends of the SW-CNT channel using an electron-beam lithography technique. A PVDF-TrFE nanodot was suspended precisely at the center of the CNT channel by dip-pen lithography (DPN) of a randomly copolymerized solution made of 70/30 mol % polyvinylidene fluoride and polytrifluoroethylene. To elaborate the DPN process, an atomically flat SiO<sub>2</sub>/Si substrate with well-aligned terraces was used. After the deposition using a sharp Si<sub>3</sub>N<sub>4</sub> DPN tip with a radius less than 10 nm, the precursor sol nanodots were slowly dried for several days at room temperature. The polymer nanodot was subsequently annealed at 140 °C for 1 h. Finally, a polymer-gate-based CNT-FeFET device in which all of the components were integrated into a single nanometer-sized piece was obtained.

Morphological features of the gate nanodots were examined using an atomic force microscope equipped with a sharp Si<sub>3</sub>N<sub>4</sub> tip, with its radius less than 10 nm. PFM and KFM studies were performed to investigate the ferroelectric switching characteristics of the nanodot by switching and subsequent reading of the ferroelectric domain under an applied electric field. A platinum-coated Si<sub>3</sub>N<sub>4</sub> conducting tip (tip radius  $\sim$ 20 nm, tip height 15  $\mu$ m, resonance frequency  $\sim$  80 kHz, and spring constant  $\sim$ 0.65 N/m; MIKROMASCH) and a constant scanning speed of 50 nm/s were used in PFM and KFM measurements. A platinum-coated conducting PFM tip was used in the PFM measurements. The channel current was measured as a function of the source-drain voltage  $(I-V_{SD} \text{ curve})$  for both upward and downward polarizations of the ferroelectric PVDF-TrFE nanodot. The bistable currents were measured as a function of the switching cycle for the two distinct resistance states (HRS and LRS) by fixing the  $V_{SD}$  value at 100 mV.

Acknowledgment. This work was supported by the Brain Korea 21 Project 2010 and by the Korea Research Foundation Grant under Contract No. KRF-2008-313-C00309. This research was also supported by the WCU (World Class University) program through the Korea Research Foundation funded by the Ministry of Education, Science and Technology (Grant No. R31-2008-000-10059-0), Republic of Korea.

Supporting Information Available: Ferroelectric hysteresis loop of the PVDF-TrFE polymer thin film, schematic drawings that illustrate the fabrication of the Au-metal gate on the polymer gate nanodot, and  $I-V_{SD}$  curves of the CNT-based nonvolatile memory device. This material is available free of charge *via* the Internet at http://pubs.acs.org.

## **REFERENCES AND NOTES**

- 1. Tans, S. J.; Verschueren, A. R. M.; Dekker, C. Room-Temperature Transistor Based on a Single Carbon Nanotube. *Nature* **1998**, *393*, 49–52.

- Bachtold, A.; Hadley, P.; Nakanishi, T.; Dekker, C. Logic Circuits with Carbon Nanotube Transistors. *Science* 2001, 294, 1317–1320.

- Heinze, S.; Tersoff, J.; Martel, R.; Derycke, V.; Appenzeller, J.; Avouris, P. Carbon Nanotubes as Schottky Barrier Transistors. *Phys. Rev. Lett.* **2002**, *89*, 106801.

- Heller, I.; Janssens, A. M.; Mannik, J.; Minot, E. D.; Lemay, S. G.; Dekker, C. Identifying the Mechanism of Biosensing with Carbon Nanotube Transistors. *Nano Lett.* **2008**, *8*, 591–595.

- Martel, R.; Schmidt, T.; Shea, H. R.; Hertel, T.; Avouris, P. Single- and Multi-Wall Carbon Nanotube Field-Effect Transistors. *Appl. Phys. Lett.* **1998**, *73*, 2447–2449.

- Baughman, R. H.; Zakhidov, A. A.; de Heer, W. A. Carbon Nanotubes—The Route toward Applications. *Science* 2002, 297, 787–792.

- Wong, E. W.; Sheehan, P. E.; Lieber, C. M. Nanobeam Mechanics: Elasticity, Strength, and Toughness of Nanorods and Nanotubes. *Science* 1997, 277, 1971–1975.

- 8. Fu, W.; Xu, Z.; Bai, X.; Gu, C.; Wang, E. Intrinsic Memory Function of Carbon Nanotube-Based Ferroelectric Field-Effect Transistor. *Nano Lett.* **2009**, *9*, 921–925.

- 9. Scott, J. F.; de Araujo, C. A. P. Ferroelectric Memories. Science **1989**, 246, 6.

- Scott, J. F. Applications of Modern Ferroelectrics. *Science* 2007, 315, 954–959.

- Shin, Y.-H.; Grinberg, I.; Chen, I. W.; Rappe, A. M. Nucleation and Growth Mechanism of Ferroelectric Domain-Wall Motion. *Nature* 2007, 449, 881–884.

- Ahn, C. H.; Tybell, T.; Antognazza, L.; Char, K.; Hammond, R. H.; Beasley, M. R.; Fischer, O.; Triscone, J. M. Nonvolatile Electronic Writing of Epitaxial Pb(Zr<sub>0.52</sub>Ti<sub>0.48</sub>)O<sub>3</sub>/SrRuO<sub>3</sub> Heterostructures. *Science* **1997**, *276*, 1100–1103.

- Luo, Y.; Szafraniak, I.; Zakharov, N. D.; Nagarajan, V.; Steinhart, M.; Wehrspohn, R. B.; Wendorff, J. H.; Ramesh, R.; Alexe, M. Nanoshell Tubes of Ferroelectric Lead Zirconate Titanate and Barium Titanate. *Appl. Phys. Lett.* 2003, *83*, 440–442.

- Lee, H. N.; Hesse, D.; Zakharov, N.; Gosele, U. Ferroelectric Bi<sub>325</sub>La<sub>0.75</sub>Ti<sub>3</sub>O<sub>12</sub> Films of Uniform a-Axis Orientation on Silicon Substrates. *Science* **2002**, *296*, 2006–2009.

- Naber, R. C. G.; Tanase, C.; Blom, P. W. M.; Gelinck, G. H.; Marsman, A. W.; Touwslager, F. J.; Setayesh, S.; de Leeuw,

D. M. High-Performance Solution-Processed Polymer Ferroelectric Field-Effect Transistors. *Nat. Mater.* **2005**, *4*, 243–248.

- Lovinger, A. J. Ferroelectric Polymers. *Science* **1983**, *220*, 1115–1121.

- Hu, Z.; Tian, M.; Nysten, B.; Jonas, A. M. Regular Arrays of Highly Ordered Ferroelectric Polymer Nanostructures for Non-volatile Low-Voltage Memories. *Nat. Mater.* 2009, *8*, 62–67.

- Son, J. Y.; Lee, G.; Jo, M.-H.; Kim, H.; Jang, H. M.; Shin, Y.-H. Heteroepitaxial Ferroelectric ZnSnO<sub>3</sub> Thin Film. *J. Am. Chem. Soc.* **2009**, *131*, 8386–8387.

- Alexe, M.; Harnagea, C.; Visinoiu, A.; Pignolet, A.; Hesse, D.; Goele, U. Patterning and Switching of Nano-Size Ferroelectric Memory Cells. *Scr. Mater.* 2001, 44, 1175–1179.

- Lee, W.; Han, H.; Lotnyk, A.; Schubert, M. A.; Senz, S.; Alexe, M.; Hesse, D.; Baik, S.; Gosele, U. Individually Addressable Epitaxial Ferroelectric Nanocapacitor Arrays with Near Tb inch<sup>-2</sup> Density. *Nat. Nanotechnol.* **2008**, *3*, 402–407.

- 21. Piner, R. D.; Zhu, J.; Xu, F.; Hong, S.; Mirkin, C. A. "Dip-Pen" Nanolithography. *Science* **1999**, *283*, 661–663.

- Basnar, B.; Willner, I. Dip-Pen-Nanolithographic Patterning of Metallic, Semiconductor, and Metal Oxide Nanostructures on Surfaces. *Small* **2009**, *5*, 28–44.

- Son, J. Y.; Shin, Y.-H.; Ryu, S.; Kim, H.; Jang, H. M. Dip-Pen Lithography of Ferroelectric PbTiO<sub>3</sub> Nanodots. J. Am. Chem. Soc. 2009, 131, 14676–14678.

- 24. Tashiro, K.; Kobayashi, M. Structural Study of the Ferroelectric Phase Transition of Vinylidene Fluoride-Trifluoroethylene Copolymers: 4. Poling Effect on Structure and Phase Transition. *Polymer* **1986**, *27*, 667–676.

- 25. Furukawa, T. Ferroelectric Properties of Vinylidene Fluoride Copolymers. *Phase Transitions* **1989**, *18*, 143–211.